- News

- 共通

名刺サイズの「CMOSアニーリングマシン」、日立が開発

名刺サイズの「CMOSアニーリングマシン」を日立製作所が開発した。組み合わせ最適化問題をスマートフォンやセンサーなどのエッジ端末で計算する可能性を高めた。NEDO(新エネルギー・産業技術総合開発機構)の委託業務の結果として2019年2月19日に発表した。

日立製作所が今回開発したCMOSアニーリングマシンは、磁性体の性質を説明するために考案された「イジングモデル」の動作をCMOS回路で再現するなどで、アニーリングマシンを91mm × 55 mmにまで小型化したもの(写真1)。交通渋滞などの組み合わせ最適化問題を、スマートフォンやカメラ、センサーといったエッジ端末でリアルタイムに計算する可能性を高めた。

高速化も図った。約6万パラメーターの組み合わせ最適化問題を従来型コンピューターの約2万倍の速さで計算する。エネルギー効率も約17万倍に向上した(汎用的なCPU「Corei7-6700K」で同条件で計算した時の比較結果)という。

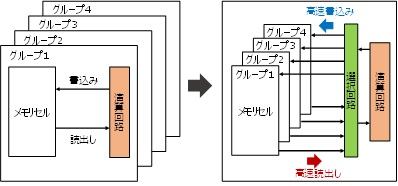

今回開発した技術の特長として日立は次の2つを挙げる。1つは回路技術。CMOSアニーリングマシンによる最適化問題の計算では、パラメーターを4グループに分け、それぞれを順次計算をする。従来、グループ数だけ演算回路を用意していたが、今回はパラメーター値を保持するメモリーセルへのデータアクセスを高速化することで、1つの演算回路をグループ間で切り替えながら共有できるようにした(図1)。

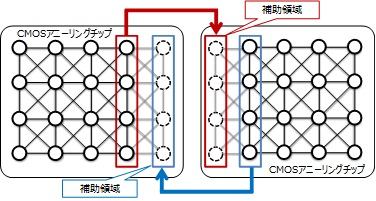

もう1つは、半導体チップ間の接続技術。最適化問題の計算では、個々のパラメーターの値と、それに隣接するパラメーターの値を用いる。従来はパラメーター値をチップ間で転送するため高速処理が困難だった。今回はチップの端部に、別チップのパラメーター値をコピーできる補助領域を設け、パラメーターグループを計算する間に次のパラメーターグループをコピーできるようにした(図2)。

名刺サイズのCMOSアニーリングマシンは、開発した技術を搭載したチップを2枚接続して実現している。